# 4.26 inch E-paper Display Series GDEQ0426T82

GooDisplay

Dalian Good Display Co., Ltd.

# **Product Specifications**

| Customer    | Standard              |

|-------------|-----------------------|

| Description | 4.26" E-PAPER DISPLAY |

| Model Name  | GDEQ0426T82           |

| Date        | 2023/02/15            |

| Revision    | 1.0                   |

|          | Design Team |      |

|----------|-------------|------|

| Approval | Check       | Edit |

| 宝刘印玉     | 燕修印凤        | 之陈印兵 |

NO.18 Zhonghua W. Rd, Ganjingzi Dist, Dalian, China

Tel: +86-411-84619565

Email: info@good-display.com

Site: www.good-display.com

# **Content**

| 1.  | Overview                                        | 4   |

|-----|-------------------------------------------------|-----|

| 2.  | Features                                        | 4   |

| 3.  | Mechanical Specification                        | 4   |

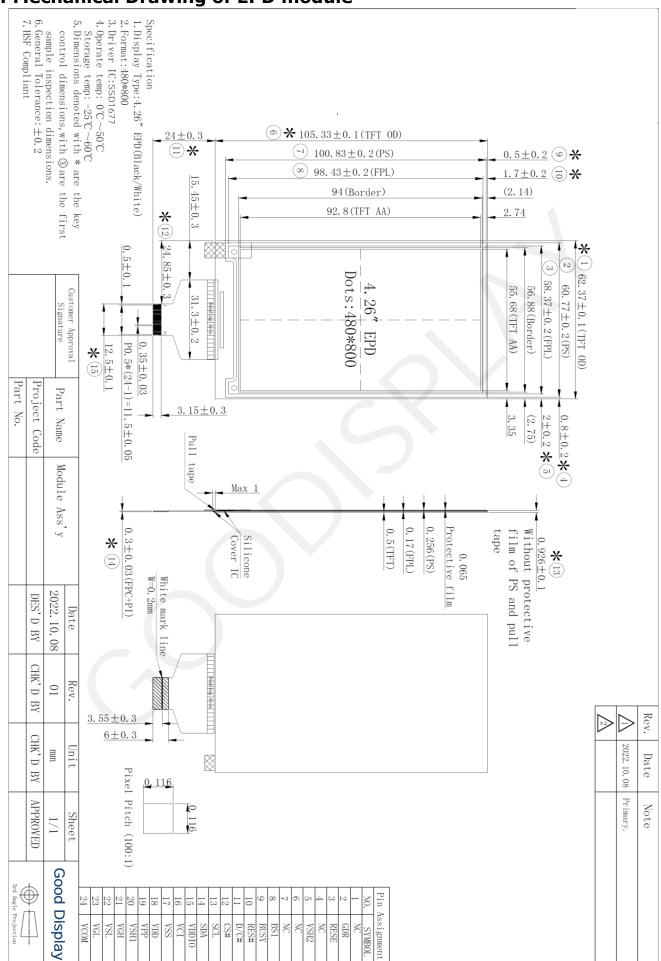

| 4.  | Mechanical Drawing of EPD Module                | . 5 |

| 5.  | Input/output Pin Assignment                     | 6   |

| 6.  | Absolute maximum rating                         | .7  |

| 7.  | Electrical Characteristics                      | 7   |

|     | 7.1 DC Characteristics                          |     |

|     | 7.2 Panel DC Characteristics                    |     |

|     | 7.3 Optical Specification                       | 8   |

|     | 7.4 AC Electrical Characteristics               | 9   |

| 8.F | unctional Specification and Application Circuit | .10 |

|     | 8.1 Power On/Off and DSLP Sequence              | .10 |

|     | 8.2 Reference Circuit                           | 11  |

| 9.M | latched Development Kit                         | .12 |

| 10. | Reliability Test                                | 13  |

| 11. | Outgoing Quality Control Specifications         | .14 |

| 12. | Handling, Safety and Environmental Requirements | 20  |

| 13. | Packing                                         | 22  |

| 11  | Procautions                                     | 22  |

#### 1 Overview

GDEQ0426T82 is a reflective electrophoretic display module on an active matrix TFT substrate, The diagonal length of the active area is 4.26" and contains 800x480 pixels. The panel is capable of displaying 1-bit black, white images depending on the associated lookup table used. The circuitry on the panel includes an integrated gate and source driver, timing controller, oscillator, DC-DC boost circuit, and memory to store the frame buffer and lookup tables, and additional circuitry to control VCOM and border settings.

#### 2 Features

- Ultra wide viewing angle

- Ultra low power consumption

- I<sup>2</sup>C Signal Master Interface to read external temperature sensor.

- On chip display RAM

- Interface :4-Wire SPI or 3-Wire SPI

- Wide range of operating temperature: 0 to 50

- Wide range of storage temperature: -25 to 60

- High reflectance and contrast TFT electrophoretic.

## 3 Mechanical Specifications

| NO. | ITEM                | SPECIFICATION                | UNIT |

|-----|---------------------|------------------------------|------|

| 1   | Dot Matrix          | 800(H)×480(V)                | -    |

| 2   | Screen Size         | 4.26                         | Inch |

| 3   | Active Area         | 92.8(H)×55.68(V)             | mm   |

| 4   | Pixel Pitch         | 0.116×0.116                  | mm   |

| 5   | Pixels Per Inch     | 219                          | -    |

| 6   | TFT Area            | 105.33(H)×62.37(V)           | mm   |

| 7   | Outline Dimension   | 129.33(H)×62.37(V) ×0.926(D) | mm   |

| 8   | Pixel Configuration | Square                       | -    |

| 9   | Driver IC           | SSD1677                      | -    |

| 10  | Module Weight       | 12.4±10%                     | gram |

4 Mechanical Drawing of EPD module

## 5. Module Interface

# PIN NO. PIN DESCRIPTION NAME

|     | NAME  |                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,4 | NC    | No Connection                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | GDR   | This pin is N-Channel MOSFET gate drive control pin.                                                                                                                                                                                                                                                                                                                                   |

| 3   | RESE  | Current Sense Input for the control loop                                                                                                                                                                                                                                                                                                                                               |

| 5   | VSH2  | This pin is Positive Source driving voltage, VSH2 Connect a stabilizing capacitor between VSH2 and VSS in the application circuit.                                                                                                                                                                                                                                                     |

| 6   | NC    | No Connection                                                                                                                                                                                                                                                                                                                                                                          |

| 7   | NC    | No Connection                                                                                                                                                                                                                                                                                                                                                                          |

| 8   | BS1   | This pin is for selecting 3-wire(H active) or 4-wire(L active) SPI interface.                                                                                                                                                                                                                                                                                                          |

| 9   | BUSY  | This pin is Busy state output pin. When Busy is High, the operation of the chip should not be interrupted, and command should not be sent. For example, The chip would output Busy pin as High when  - Outputting display waveform; or  - Programming with OTP  Communicating with digital temperature sensor In the cascade mode, the BUSY pin of the slave chip should be left open. |

| 10  | RES#  | This pin is reset signal input (Active Low).                                                                                                                                                                                                                                                                                                                                           |

| 11  | D/C#  | This pin is Data/Command control pin connecting to the MCU                                                                                                                                                                                                                                                                                                                             |

| 12  | CS#   | This pin is the chip select input connecting to the MCU.                                                                                                                                                                                                                                                                                                                               |

| 13  | SCL   | This pin is serial clock pin for interface.                                                                                                                                                                                                                                                                                                                                            |

| 14  | SDA   | This pin is serial data pin for interface.                                                                                                                                                                                                                                                                                                                                             |

| 15  | VDDIO | Power for interface logic pins                                                                                                                                                                                                                                                                                                                                                         |

| 16  | VCI   | Power input pin for the chip.                                                                                                                                                                                                                                                                                                                                                          |

| 17  | VSS   | Ground                                                                                                                                                                                                                                                                                                                                                                                 |

| 18  | VDD   | Core logic power pin VDD can be regulated internally from VCI. A capacitor should be connected between VDD and VSS under all circumstances                                                                                                                                                                                                                                             |

| 19  | VPP   | Power Supply for OTP Programming.                                                                                                                                                                                                                                                                                                                                                      |

| 20  | VSH1  | This pin is Positive Source driving voltage, VSH1 Connect a stabilizing capacitor between VSH1 and VSS in the application circuit.                                                                                                                                                                                                                                                     |

| 21  | VGH   | This pin is Positive Gate driving voltage. Connect a stabilizing capacitor between VGH and VSS in the application circuit.                                                                                                                                                                                                                                                             |

| 22  | VSL   | This pin is Negative Source driving voltage. Connect a stabilizing capacitor between VSL and VSS in the application circuit.                                                                                                                                                                                                                                                           |

| 23  | VGL   | This pin is Negative Gate driving voltage. Connect a stabilizing capacitor between VGL and VSS in the application circuit.                                                                                                                                                                                                                                                             |

| 24  | VCOM  | This pins is VCOM driving voltage Connect a stabilizing capacitor between VCOM and VSS in the application circuit.                                                                                                                                                                                                                                                                     |

#### 6 Absolute Maximum Ratings

| ITEM                 | SYMBOL | MIN  | MAX       | UNIT | REMARK |

|----------------------|--------|------|-----------|------|--------|

| Logic supply voltage | VCI    | -0.5 | +4.0      | V    | -      |

| Logic Input voltage  | VIN    | -0.5 | VDDIO+0.5 | V    | -      |

| Logic Output voltage | VOUT   | -0.5 | VDDIO+0.5 | V    | -      |

| Operating Temp.      | Тор    | 0    | +50       | С    | -      |

| Storage Temp         | Tstg   | -25  | +60       | С    | -      |

Note (1): All of the voltages are on the basis of "VSS = 0V".

Note (2): Maximum ratings are those values beyond which damages to the device may occur. Functional operation should be restricted to the limits in the Panel DC Characteristics tables.

#### 7 Electrical Characteristics

#### 7.1 DC Characteristics

The following specifications apply for: VSS=0V, VCI=3.3V, TOPR =25°C.

| Parameter                              | Symbol            | Condition                                                              | Applicabl<br>e pin | Min.      | Тур. | Max.      | Unit |

|----------------------------------------|-------------------|------------------------------------------------------------------------|--------------------|-----------|------|-----------|------|

| VCI operation voltage                  | VCI               | -                                                                      | _                  | 2.2       | 3.0  | 3.3       | V    |

| High level input voltage               | $V_{ m IH}$       | Digital input pins                                                     | -                  | 0.8*VDDIO | -    | VDDIO     | V    |

| Low level input voltage                | $V_{\rm IL}$      | Digital input pins                                                     | -                  | 0         | -    | 0.2*VDDIO | V    |

| High level output voltage              | Vон               | I <sub>OH</sub> = - 100uA                                              | -                  | 0.9*VDDIO | -    | -         | V    |

| Low level output voltage               | V <sub>OL</sub>   | $I_{OL} = 100uA$                                                       | _                  | _         | -    | 0.1*VDDIO | V    |

| OTP Program voltage                    | VPP               | -                                                                      | _                  | 7.25      | 7.5  | 7.75      | V    |

| Typical power panel                    | P <sub>TYP</sub>  | VCI=3.3V                                                               | _                  | _         | TBD  | -         | mW   |

| Standby power panel                    | P <sub>STPY</sub> | VCI=3.3V                                                               | -                  | _         | TBD  | _         | mW   |

| Typical operating current(white state) | Iopr_VCI          | VCI=3.3V                                                               | -                  | -         | TBD  | -         | mA   |

| Full update time                       | -                 | 23° C                                                                  | -                  | -         | 4    | -         | sec  |

| Fast update time                       | -                 | 23° C                                                                  | -                  | -         | 1    | -         | sec  |

| Partial update time                    | -                 | 23° C                                                                  | -                  | -         | 0.76 | -         | sec  |

| Sleep mode current                     | Islp_VCI          | VCI=3.3V<br>DC/DC OFF<br>No clock<br>No output load<br>Ram data retain | VCI                | -         | 40   | 70        | uA   |

| Deep sleep mode current                | Idslp_VCI         | VDD OFF                                                                | VCI                | -         | 2    | 6         | uA   |

Note: The VDD, VCI input must be kept in a stable value; ripple and noise are not allowed.

#### 7.2 Panel DC Characteristics (Driver IC Internal Regulators)

The following specifications apply for: VSS=0V, VCI=3.3V, TOPR =25°C.

| Parameter                      | Symbol   | Condition | Applicable pin      | Min.  | Тур. | Max.  | Unit |

|--------------------------------|----------|-----------|---------------------|-------|------|-------|------|

| VCOM output voltage            | VCOM     | -         | VCOM                | -     | -2.0 | -     | V    |

| Positive Source output voltage | $V_{SH}$ | -         | S0~S479             | -     | 15   | -     | V    |

| Negative Source output voltage | $V_{SL}$ | -         | S0~S479             | -     | -15  | -     | V    |

| Positive gate output voltage   | Vgh      | -         | G0~G <sub>799</sub> | 19.5  | 20   | 20.5  | V    |

| Negative gate output voltage   | Vgl      | -         | G0~G <sub>799</sub> | -19.5 | -20  | -20.5 | V    |

### 7.3 Optical Specification

Measurements are made with that the illumination is under an angle of 45 degree, the detection is perpendicular unless otherwise specified.

| Symbol   | Parameter          | Conditions | Min | Тур.                        | Max | Units | Notes  |

|----------|--------------------|------------|-----|-----------------------------|-----|-------|--------|

| R        | White Reflectivity | White      | 30  | 35                          | -   | %     | Note 1 |

| CR       | Contrast Ratio     | indoor     | 8:1 | -                           | -   | -     | Note 2 |

| T update | Image update time  | 23 °C      | -   | 4                           | -   | sec   | -      |

| Tlife    | Life               | Topr       |     | 1000000 times<br>or 5 years | -   | -     | -      |

Notes1: Luminance meter: Eye-One Pro Spectrophotometer.

Notes2:CR=Surface Reflectance with all white pixel/Surface Reflectance with all black pixels.

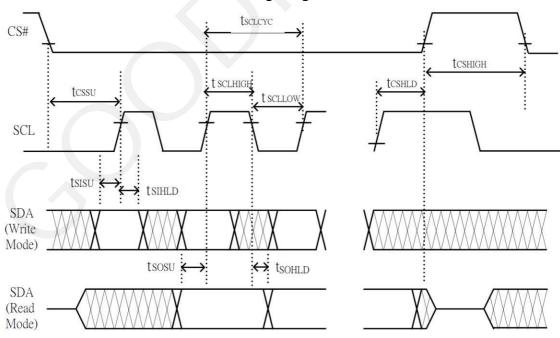

#### 7.4 AC Electrical Characteristics

The following specifications apply for: VDDIO - VSS = 2.2V to 3.7V, TOPR =  $25^{\circ}$ C, CL=20Pf

#### Write mode

| Symbol   | Parameter                                                                    | Min | Тур | Max | Unit |

|----------|------------------------------------------------------------------------------|-----|-----|-----|------|

| fscL     | SCL frequency (Write Mode)                                                   |     |     | 20  | MHz  |

| tcssu    | Time CS# has to be low before the first rising edge of SCLK                  | 20  |     |     | ns   |

| tcshld   | Time CS# has to remain low after the last falling edge of SCLK               | 20  |     |     | ns   |

| tcsнigh  | Time CS# has to remain high between two transfers                            | 100 |     |     | ns   |

| tsclcyc  | SCL cycle time                                                               | 50  |     |     | ns   |

| tsclhigh | Part of the clock period where SCL has to remain high                        | 25  |     |     | ns   |

| tscllow  | Part of the clock period where SCL has to remain low                         | 25  |     |     | ns   |

| tsisu    | Time SI (SDA Write Mode) has to be stable before the next rising edge of SCL | 10  |     |     | ns   |

| tsihld   | Time SI (SDA Write Mode) has to remain stable after the rising edge of SCL   | 40  |     |     | ns   |

#### Read mode

| Symbol   | Parameter                                                                | Min | Тур  | Max | Unit |

|----------|--------------------------------------------------------------------------|-----|------|-----|------|

| fscL     | SCL frequency (Read Mode)                                                |     |      | 2.5 | MHz  |

| tcssu    | Time CS# has to be low before the first rising edge of SCLK              | 100 |      |     | ns   |

| tcshld   | Time CS# has to remain low after the last falling edge of SCLK           | 50  |      |     | ns   |

| tcsнigh  | Time CS# has to remain high between two transfers                        | 250 | =1 % |     | ns   |

| tsclhigh | Part of the clock period where SCL has to remain high                    | 180 |      |     | ns   |

| tscllow  | Part of the clock period where SCL has to remain low                     | 180 |      |     | ns   |

| tsosu    | Time SO(SDA Read Mode) will be stable before the next rising edge of SCL | 3   | 50   |     | ns   |

| tsohld   | Time SO (SDA Read Mode) will remain stable after the falling edge of SCL |     | 0    |     | ns   |

Note: All timings are based on 20% to 80% of VDDIO-VSS

#### SPI timing diagram

SPI interface timing

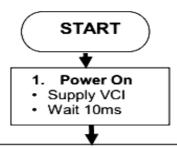

#### 8 Functional Specification and Application Circuit

#### 8.1 Power On/Off and DSLP Sequence

General operation flow to drive display panel

#### 2. Set Initial Configuration

- · Define SPI interface to communicate with MCU

- HW Reset

- SW Reset by Command 0x12

- Wait 10ms

#### 3. Send Initialization Code

- Clear and fill two RAM by Command 0x46, Data 0XF7 for RAM 0x24 and Command 0x47, Data 0xF7 for RAM 0x26

- Set gate driver output by Command 0x01

- Set display RAM size by Command 0x11, 0x44, 0x45

- Set panel border by Command 0x3C

#### 4. Load Waveform LUT

- Sense temperature by int/ext TS by Command 0x18

- Load waveform LUT from OTP by Command 0x22, 0x20 or by MCU

- Wait BUSY Low

#### 5. Write Image and Drive Display Panel

- Write image data in RAM by Command 0x4E, 0x4F, 0x24, 0x26

- · Set softstart setting by Command 0x0C

- Drive display panel by Command 0x22, 0x20

- Wait BUSY Low

#### 6. Power Off

- Deep sleep by Command 0x10

- Power OFF

END

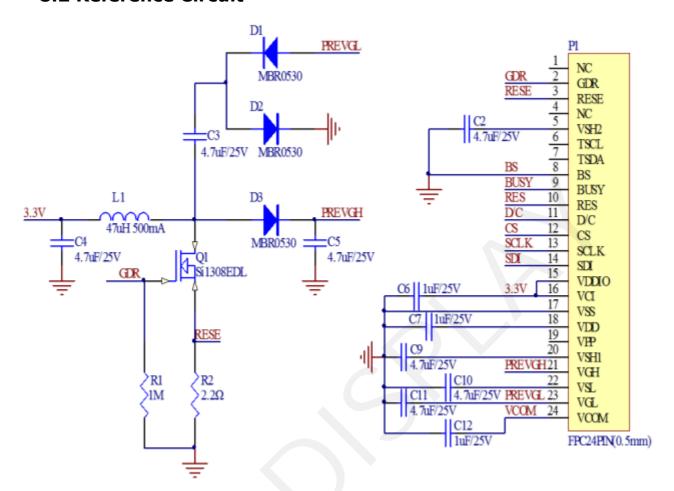

#### **8.2 Reference Circuit**

#### 9 Matched Development Kit

Our Development Kit designed for SPI E-paper Display aims to help users to learn how to use E-paper Display more easily. It can refresh black-white E-paper Display and three-color (black, white and red/Yellow) Good Display 's E-paper Display. And it is also added the functions of USB serial port, Raspberry Pi and LED indicator light ect.

DESPI Development Kit consists of the development board and the pinboard . More details about the Development Kit, please click to the following link:

https://www.good-display.com/product/219.html

#### 10 Reliability

| NO | Test items                                  | Test condition                                                                                                                             | QUANTITY |

|----|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1  | Low-Temperature<br>Storage                  | $T=-25^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                                    | 5pcs     |

| 2  | Low-Temperature<br>Operation                | $T=0^{\circ}C$ , 240 h;<br>Put the product into the experimental procedure, run it in the temperature box, and check it every 24 hours.    | 5pcs     |

| 3  | High-Temperature<br>Operation               | T = 40°C, RH = 35%, 240 h;<br>Put the product into the experimental procedure, run it in the temperature box, and check it every 24 hours. | 5pcs     |

| 4  | High-Temperature<br>Storage                 | T=60°C, RH=35%;<br>White screen state, for 240h.                                                                                           | 5pcs     |

| 5  | Temperature<br>Cycle                        | 1 cycle:[-25°C 30min]→[+60 °C 30 min];<br>100 cycles.                                                                                      | 5pcs     |

| 6  | High-Temperature/<br>High- humidity Storage | T=50°C, RH=90%;<br>White screen state, for 240h.                                                                                           | 5pcs     |

| 7  | UV exposure Resistance                      | 765W/m <sup>2</sup> for 168hrs,T = 40°C, RH=35%;                                                                                           | 5pcs     |

| 8  | ESD Contact discharge                       | $\pm 200$ V, Test 5 point; Each point discharge 10 times. Time interval is not less than 1 second.                                         | 5pcs     |

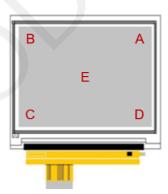

#### **ESD** test location

#### **Test and measurement conditions**

After the end of the experiment, the sample was taken out of the temperature chamber, and stood at room temperature for 1h, and then the sample was inspected for appearance, function and optical inspection.

#### Criteria for qualification (pass the test if all qualified):

- (1) The product can be normal refresh.

- (2) There are no new point defects or line defects in the display screen.

- (3) discoloration, blurred handwriting and barcode can be read on the complex screen.

#### 11 Outgoing Quality Control Specifications

#### 11.1 Sampling Method

(1) GB/T 2828.1, inspection level II, normal inspection, single sample inspection

(2) AQL: Major 0.4; Minor 0.65

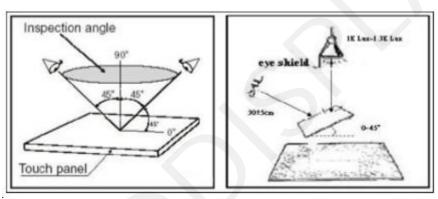

#### 11.2 Inspection Conditions

The environmental conditions for test and measurement are

performed as follows. Temperature: 23±3°C

Humidity: 55±15%R.H

Inspection of illuminance: 800~1500Lux Inspection time: signal face 5S-10S

Distance between the Panel & Eyes: 30±10cm

Viewing angle from the vertical in each direction: ±45°

(See the sketch below)

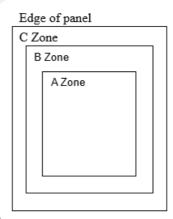

#### 11.3 Quality Assurance Zones

Zone A: Active Area

Zone B: Black Frame Area

Zone C: Outside Black Frame Area

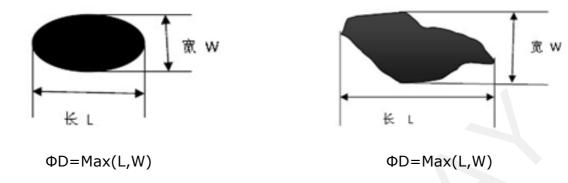

#### 11.4 Inspection Standard

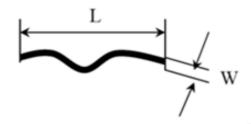

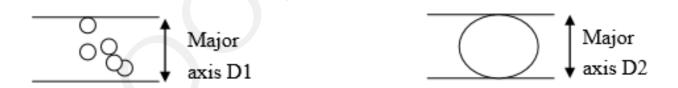

Defects Definition of Φ&L&W (Unit: mm)

#### 11.4.1 Dot defects:

#### 11.4.2 line defect:

# 11.4.3 Small bubble aggregation and large bubble definition:

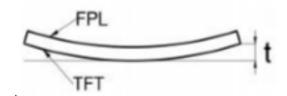

# 11.4.4 TFT warpage:

# 11.5 Appearance Defects

| NO.   | ITEM                                                                                 | CRITERIA                                                                                                                  | Acceptable range | Method                                          | Defect<br>level | Area        |

|-------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------|-----------------|-------------|

| 1     | Spotty (black<br>spots, white<br>spots, foreign<br>bodies, air<br>bubbles,<br>bumps) | D≦0.25mm                                                                                                                  | Ignore           | Film<br>Card                                    | Minor           | Zone<br>A   |

|       |                                                                                      | 0.25mm < D ≤ 0.5 mm, Distance≥5mm                                                                                         | <b>N</b> ≦ 4     |                                                 |                 |             |

|       |                                                                                      | D>0.5 mm                                                                                                                  | N=0              |                                                 |                 |             |

|       |                                                                                      | 0.1mm< D≤ 0.25 mm(Dense point)                                                                                            | N≦ 3/cm2         |                                                 |                 |             |

|       | POOR<br>LINEAR<br>SHAPE<br>(foreign body,<br>glass scratch)                          | $L \leq 2mm, W \leq 0.1mm$                                                                                                | Ignore           | Film<br>Card                                    | Minor           | Zone<br>A   |

|       |                                                                                      | $2 \text{mm} < L \le 8 \text{mm}, \ 0.1 < W \le 0.5 \text{mm}$                                                            | N≦4              |                                                 |                 |             |

| 2     |                                                                                      | L>8mm, W>0.5mm<br>Note: FPL Lacerations are not allowed                                                                   | N=0              |                                                 |                 |             |

|       | steel pit                                                                            | Long strip pits are not allowed                                                                                           | N=0              | Sight<br>Check                                  | Minor           | Zone<br>A   |

| 3     | Glass Crack                                                                          | Extensional cracks are not allowed                                                                                        | N=0              | Sight<br>Check                                  | Major           | Zone<br>B,C |

| 4     | Edge breakage                                                                        | X≤3mm,Y≤0.5mm, It does not affect the electrode                                                                           | N≦2              | Sight<br>Check/<br><u>Microsc</u><br><u>ope</u> | Minor           | Zone<br>C   |

| 5     | Chip Package<br>Chip Off                                                             | X≤2mm · Y≤2mm, It does not affect the electrode(FPC edge)  X≤1mm · Y≤1mm, It does not affect the electrode((Not FPC edge) | N≦2              | Sight<br>Check/<br><u>Microsc</u><br><u>ope</u> | Minor           | Zone<br>C   |

| 6     | Dirt                                                                                 | No dirt (finger print, dust, residual glue, etc.)                                                                         | Ignore           | Sight<br>Check                                  | Minor           | Zone<br>A,B |

|       | Silicone                                                                             | The maximum diameter of a single bubble cannot exceed 2mm                                                                 | N≤2              | Sight Check/ Film card                          |                 | Zone<br>C   |

| 7     |                                                                                      | Crack is not allowed and there are no visible impurities in the glue of the lead part                                     | N=0              |                                                 | Minor           |             |

| ,<br> |                                                                                      | The adhesive must completely cover the ACF, lead area and IC and should be applied evenly                                 | N=0              |                                                 |                 |             |

| NO. | ITEM                     | CRITERIA                                                                                                                                | Acceptable range | Method                 | Defect<br>level | Area        |

|-----|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|-----------------|-------------|

|     |                          | No glue leakage, no obvious lack of glue in the lead area                                                                               | N=0              |                        |                 |             |

|     |                          | Glue height exceeds PS surface                                                                                                          | N=0              |                        |                 |             |

|     |                          | FPC Front overflow glue width>0.5mm or<br>Back side overflow glue width>1mm                                                             | N=0              |                        |                 |             |

|     | Edge Sealing<br>Adhesive | No glue leakage                                                                                                                         | N=0              | Sight Check/ Film card | Major           | Zone<br>C   |

| 8   |                          | The height of sealant exceeds PS surface                                                                                                | N=0              |                        | Minor           |             |

|     |                          | The edge sealing adhesive shall not leak the TFT glass substrate                                                                        | N=0              |                        |                 |             |

|     |                          | Judging Ok of water-blocking area ≥ 0.7<br>mm of PS edge sealant                                                                        | N=0              |                        | Minor           |             |

|     | Protective film          | Foreign body in protective film                                                                                                         | N=0              | Sight                  |                 | Zone<br>A   |

| 9   |                          | The protective film punctures and injures FPL                                                                                           | N=0              | Check                  | Minor           |             |

| 10  | Pull Tape                | Attachment position is wrong Cannot tear up the protective film                                                                         | N=0              | Sight<br>Check         | Minor           | Zone<br>C   |

| 11  | FPC                      | FPC has break, scratch, gold finger stripping or oxidation, dirty, residual glue                                                        | N=0              | Sight<br>Check         | Major           | Zone<br>C   |

| 12  | Glass edge<br>bulge      | X≤3mm · Y≤0.3mm                                                                                                                         | N ≦ 1            | Sight<br>Check         | Minor           | Zone<br>C   |

| 13  | Warping                  | t > 1mm (3.5inch below)<br>t > 3mm (3.5inch above)                                                                                      | N=0              | Plug<br>Gage           | Minor           | Zone<br>C   |

|     | Chromatism               | Color difference in silver paste area (Not in Zone A)                                                                                   | Ignore           | Sight<br>Check         | Minor           | Zone<br>C   |

| 14  |                          | FPL Peeling occurs, chromatic aberration occurs                                                                                         | N=0              | Sight<br>Check         | Major           | Zone<br>A,B |

|     |                          | The color difference of side loss of FPL in zone B $\geq 1/2$ width                                                                     | N=0              | Sight<br>Check         | Major           | Zone<br>A,B |

| 15  | Silver pulp point        | FPL and TFT substrate conduction, silver point <1.0mm (Both single silver point and double silver point should meet this specification) | N=0              | Film<br>card           | Major           | Zone<br>C   |

| 16  | Inkjet code              | The ink jet printing font is clear, identifiable, and cannot be missing                                                                 | N=0              | Sight<br>Check         | Minor           | Zone<br>C   |

# 11.6 Displaying Defects

| NO. | ITEM                                                | CRITERIA                                                                             | Acceptable range | Method         | Defect<br>level | Area      |

|-----|-----------------------------------------------------|--------------------------------------------------------------------------------------|------------------|----------------|-----------------|-----------|

| 1   | Poor DOT<br>SHAPE (black,<br>white, group<br>White) | D≦0.25mm                                                                             | Ignore           | Film<br>Card   | Major           |           |

|     |                                                     | 0.25mm < D ≤ 0.5mm, Distance≥5mm                                                     | N≦4              |                |                 | Zone<br>A |

|     |                                                     | D>0.5mm                                                                              | N=0              |                |                 |           |

|     |                                                     | 0.1mm< D≦ 0.25 mm(Dense point)                                                       | N≦ 3/cm2         |                |                 |           |

| 2   | Line defects                                        | White or black lines running through the entire screen under any operation interface | N=0              | Sight<br>Check | Major           | Zone<br>A |

| 3   | ghost                                               | Ghosts appear only during screen switching                                           | Ignore           | Sight<br>Check | Major           | Zone<br>A |

| 4   | Flash Point                                         | Flash point occurs during screen switching only                                      | Ignore           | Sight<br>Check | Major           | Zone<br>A |

| 5   | Flash Line                                          | Flash line occurs during screen switching only                                       | N=0              | Sight<br>Check | Major           | Zone<br>A |

| 6   | Display screen<br>error                             | Unable to display a fixed screen correctly                                           | N=0              | Sight<br>Check | Major           | Zone<br>A |

| 7   | Display abnormal                                    | No display, The red matrix darkens, Note fuzzy, bar code can not be scanned,         | N=0              | Sight<br>Check | Major           | Zone<br>A |

| 8   | Residual image                                      | Residual Image Inspection (visual, final judgment reference optical specification)   | N=0              | Sight<br>Check | Major           | Zone<br>A |

| 9   | Mura Anomaly                                        | White/gray. Mura doesn't allow it                                                    | N=0              | Sight<br>Check | Major           | Zone<br>A |

# 11.7 Identification and packaging inspection

| NO. | ITEM                                                                                                                                                                                                                                                                                                                                    | CRITERIA                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | Defect<br>level |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|

| 1   | Package                                                                                                                                                                                                                                                                                                                                 | <ul> <li>(1). The products are completely placed in the anti-static tray without overlapping.</li> <li>(2). Products with different models cannot be mixed in one internal packaging bag.</li> <li>(3) There is a desiccant in the packaging bag, with good internal packaging and no expansion of the packaging bag.</li> <li>(4) The Tray model, quantity and way used for packaging meet the requirements of product specifications.</li> </ul> |                | Minor           |

| 2   | Inner and outer packing                                                                                                                                                                                                                                                                                                                 | er (1) No obvious deformation, damage, dampness or dirt on the packing case; (2) The type, quantity and method of the packing case used shall meet the requirements of the product specification. (3) There is no font or unclear design in the outer packing box.                                                                                                                                                                                 |                | Minor           |

| 3   | (1). Any unnecessary marks or marks are not allowed to exist; (2). The label information such as model, specification, quantity, weight, material number, month label and environmental protection label should be clear and correct, which should be in line with product specifications or marked according to customer requirements. |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Sight<br>Check | Minor           |

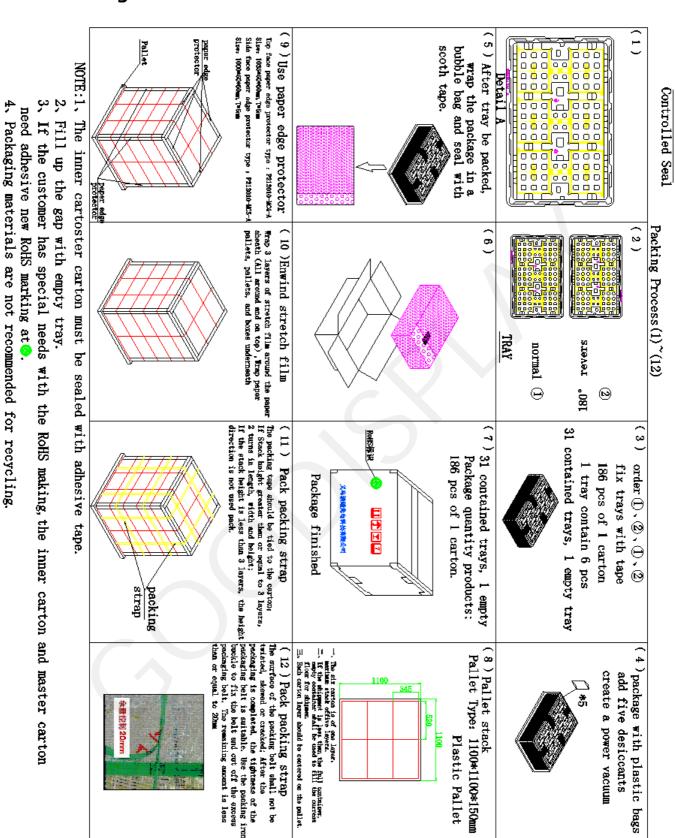

#### 12 Packing

#### 13 Environmental

#### 13.1 Handling, Safety and Environmental Requirements

#### WARNING

The display glass may break when it is dropped or bumped on a hard surface. Handle with care. Should the display break, do not touch the electrophoretic material. In case of contact with electrophoretic material, wash with water and soap.

#### **CAUTION**

The display module should not be exposed to harmful gases, such as acid and alkali gases, which corrode electronic components.

Disassembling the display module can cause permanent damage and invalidate the warranty agreements.

IPA solvent can only be applied on active area and the back of a glass. For the rest part, it is not allowed.

Observe general precautions that are common to handling delicate electronic components. The glass can break and front surfaces can easily be damaged.

Moreover the display is sensitive to static electricity and other rough environmental conditions.

#### **Mounting Precautions**

- (1) It's recommended that you consider the mounting structure so that uneven force (ex. Twisted stress) is not applied to the module.

- (2) It's recommended that you attach a transparent protective plate to the surface in order to protect the EPD. Transparent protective plate should have sufficient strength in order to resist external force.

- (3) You should adopt radiation structure to satisfy the temperature specification.

- (4) Acetic acid type and chlorine type materials for the cover case are not desirable because the former generates corrosive gas of attacking the PS at high temperature and the latter causes circuit break by electro-chemical reaction.

- (5) Do not touch, push or rub the exposed PS with glass, tweezers or anything harder than HB pencil lead. And please do not rub with dust clothes with chemical treatment. Do not touch the surface of PS for bare hand or greasy cloth. (Some cosmetics deteriorate the PS)

- (6) When the surface becomes dusty, please wipe gently with absorbent cotton or other soft materials like chamois soaks with petroleum benzene. Normal-hexane is recommended for cleaning the adhesives used to attach the PS. Do not use acetone, toluene and alcohol because they cause chemical damage to the PS.

- (7) Wipe off saliva or water drops as soon as possible. Their long time contact with PS causes deformations and color fading.

Product specification The data sheet contains final product specifications.

#### **Limiting values**

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and dose not form part of the specification.

#### **Product Environmental certification**

**ROHS**

#### REMARK

All The specifications listed in this document are guaranteed for module only. Post-assembled operation or component(s) may impact module performance or cause unexpected effect or damage and therefore listed specifications is not warranted after any Post-assembled operation.

#### 14 Precautions

- (1) Do not apply pressure to the EPD panel in order to prevent damaging it.

- (2) Do not connect or disconnect the interface connector while the EPD panel is in operation.

- (3) Do not touch IC bonding area. It may scratch TFT lead or damage IC function.

- (4) Please be mindful of moisture to avoid its penetration into the EPD panel, which may cause damage during operation.

- (5) If the EPD Panel / Module is not refreshed every 24 hours, a phenomena known as "Ghosting" or "Image Sticking" may occur. It is recommended to refreshed the ESL /EPD Tag every 24 hours in use case. It is recommended that customer ships or stores the ESL / EPD Tag with a completely white image to avoid this issue

- (6) High temperature, high humidity, sunlight or fluorescent light may degrade the EPD panel's performance. Please do not expose the unprotected EPD panel to high temperature, high humidity, sunlight, or fluorescent for long periods of time.

- (7) For more precautions, please click on the link: https://www.good-display.com/news/80.html